The Importance of Load Boards in Semiconductor Testing

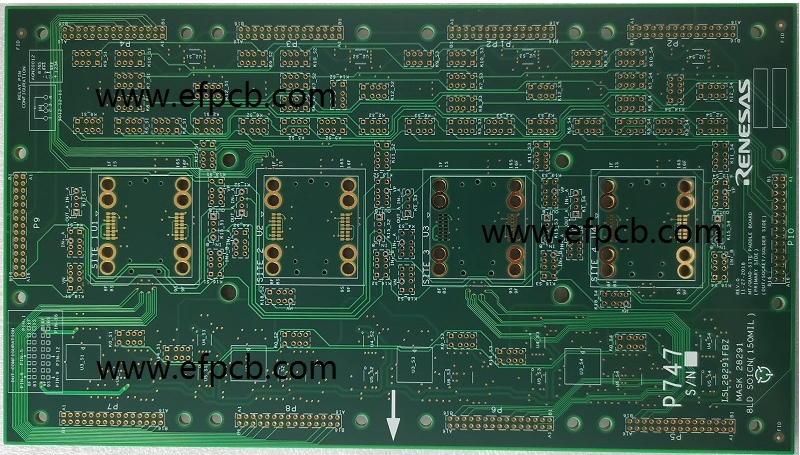

The Heap Board (LB) is a specially designed PCB that goes about as a mechanical and electrical association between the analyzer (ATE) and the gear being tested. Load Sheets have obvious actual aspects and should fit precisely inside the analyzer. As a rule, a heap board comprises of two connection points: One point of interaction face up to the analyzer's overseer unit. The hander is a robotized pick-and-spot unit that eliminates the DUT from the plate and embeds it into the attachment. The subsequent connection point focuses descending to the analyzer's pogo pins. These are the analyzer's IO ports, which electrically interface the analyzer to the DUT.

Load Board Properties

A very much constructed LB is electrically imperceptible and adds no twisting or deferral to the DUT signals. The Heap Board ought to be equipped for supporting all tests performed on the analyzer and be adequately versatile to oblige future testing (for instance, by extending the test answer for incorporate quad equal testing).

Many test engineers mean to keep all dynamic parts off the LB and simply have the latent parts expected to empower the ASIC usefulness. The pattern of working on the Heap Board originates from the longing to diminish the probability of a breakdown during the assembling stage, which could cause the creation line to stop. The time it takes to fix an issue emerges when the Heap Load up is refined.

Various tests (ATEs) need changing LB sizes. Nonetheless, all Heap Sheets comprise of similar components:

- Attachment for DUT ASIC with interface cushions for analyzer

- Stiffener increments mechanical strength.

- A few parts in view of DUT needs (R, C, and so on.)

- Connectors for the Investigate stage

In specific conditions, as well as being a connection point board, the LB may likewise remember for board testing abilities. At the point when the analyzer alone can't uphold a specific testing task, it very well may be led straightforwardly on the LB.

Configuration rules for the heap board

A Heap Board might be planned by practically any format or PCB engineer; the just required is an essential handle of the test and Burden Board ideas. A LB is frequently made out of RF4 material and is incredibly thick, with at least 20 layers.

Load Board plan contemplations are tantamount to those for other PCBs. Power supply appropriation, clock signal directing, rapid transmission steering, signal trustworthiness, wire length — these plan standards apply here too. In certain conditions, it is judicious to do some electrical feeling, especially to guarantee RF signal execution.

After the format is achieved, the accompanying step is to make/manufacture the board benefits and collect the board with the different inactive or dynamic parts and attachments.

The heap board is a urgent part of the ASIC testing framework. Make a solid yet straightforward plan to guarantee less assembling issues; save one board as a reinforcement if conceivable.

While there has forever been a necessity for load board confirmation, the shift to surface-mount innovation (SMT) has expanded the interest. IC test attachments with spring tests have acquainted an enormous electromechanical contact with the test connector gathering, which can possibly adversely influence IC bundle test exactness and trustworthiness.

A heap board, otherwise called a test interface unit or an exhibition board, interfaces the coordinated circuit under test to the test top of the parametric analyzer or robotized test hardware (ATE). A heap barricade is frequently made of a test attachment or contactor that holds an IC and joins to a printed circuit board (PCB), otherwise called a DUT or ATE board, which interfaces with an ATE's test head.

Preferably, the heap board fills in as a basically straightforward mechanical and electrical contact between the IC and the ATE. This accommodates exact and dependable assessment of IC circuit respectability and execution.

Testing a heap load up for coherence prior to utilizing it to test an incorporated circuit can set aside time and cash.

Load Board Confirmation

There are three significant methodologies for confirming burden board execution. The most essential technique is manual check. In this kind of testing, an ohmmeter searches for shorts or openings between the test attachment to-IC and PCB-to-ATE associations.

While this strategy of testing has constraints, it tends to be practical for gadgets with a low pin count, typically under 50. Nonetheless, this test approach is neither practicable nor savvy for complex frameworks with many associations.

On the far edge of the range, you might use a similar million-dollar ATE you use for gadget testing to approve the heap board. This technique is costly, wasteful, and may waste basic test assets. Regardless of whether the ATE isn't completely utilized for IC testing, additional product and different changes might be expected to help load board confirmation.

A third choice utilizes a particular burden board testing framework. It for the most part has a lower cost than ATE and a quicker and more solid testing process than manual testing.

A particular test framework, like manual or ATE load board confirmation, screens opposition and spillage flows to guarantee that there are no open or shortcircuits in the connection point hardware. A specific framework screens circuit obstruction, spillage flows, and capacitance and looks at them to known qualities.

The test framework additionally assesses the presentation of different rectifier diodes, zener diodes, and transport blends. Moreover, framework choices can uphold the testing of transfers and high-voltage parts that might be remembered for the heap board hardware.

One generally mentioned point is whether impedance ought to be assessed as a component of the heap board test. Impedance and spread delays are a consequence of the DUT load up plan process, which incorporates testing utilizing time-space reflect meters.

A particular burden board test framework's flexibility in copying various test heads is a key component. It should give an extensive variety of test-head test systems to precisely check the exhibition of burden sheets for different ATE types.

A test framework's adaptability and flexibility are firmly connected with how rapidly and effectively one test-head test system might be supplanted by another. A specific test framework is set in a producer's support office as opposed to on the test floor, so devices and other symptomatic hardware are effectively open, saving significantly additional time.

A particular burden board test framework likewise gives a few recreation prospects. A test can be placed into a contactor or test attachment to play out a highlight point obstruction test between the attachment contacts and the PCB test-head contacts. This methodology guarantees great attachment to-PCB end, which is especially basic when the attachment is connected to the PCB.

On the other hand, introduce a shorted gadget in the attachment. This approach utilizes an equal return-way obstruction test to confirm progression. At long last, a custom gadget test system, frequently given by the IC creator, may check coherence utilizing a daisy-chain obstruction test.

A particular burden board test framework is likewise helpful for assessing and supplanting spring contactors in SMT attachments. The SMT points of interaction might be tried utilizing a contact obstruction installation prior to being joined to the heap board. The apparatus likewise empowers disconnected analysis and substitution of failing spring contactors.

As semiconductor fashioners keep on incorporating ICs that load more hardware into more modest spaces with more noteworthy pin counts and more tight pitches, affirming IC bundle execution will turn out to be progressively troublesome. Confirming the heap load up prior to using it for IC testing can set aside both time and cash. Utilizing committed load board test hardware likewise checks the exhibition of different burden board plans with a more extensive estimation range. At last, it will empower the putting away and correlation of estimation information to work out load up support and substitution schedules.

- 1Understanding UL 94V-0 Flammability Rating for Printed Circuit Boards (PCBs)

- 2Top 10 Flexible PCB Factories in 2025

- 3HDI PCB Market Outlook 2025: Future Prospects, Growth Analysis & Innovations

- 4HDI PCB Design Comprehensive Guide: Mastering High Density Interconnect Technology in 2025

- 5Top HDI PCB Manufacturers (2024)

- 6IC Substrate | Comprehensive Guide (2021)

- 7PCB core raw material CCL

- 8How to Make mSAP PCB?

- 9Top 10 IC Substrate Fabricators (2024)

- 10What is IPC 4761 Type VII Via in Pad PCB?

- Skype ID: shawnwang2006

- Phone No。: +86-755-23724206

- Email: sales@efpcb.com

- Quick Contact