Semiconductor Test Boards: Ensuring Quality in Chip Testing

Keywords: semiconductor test board

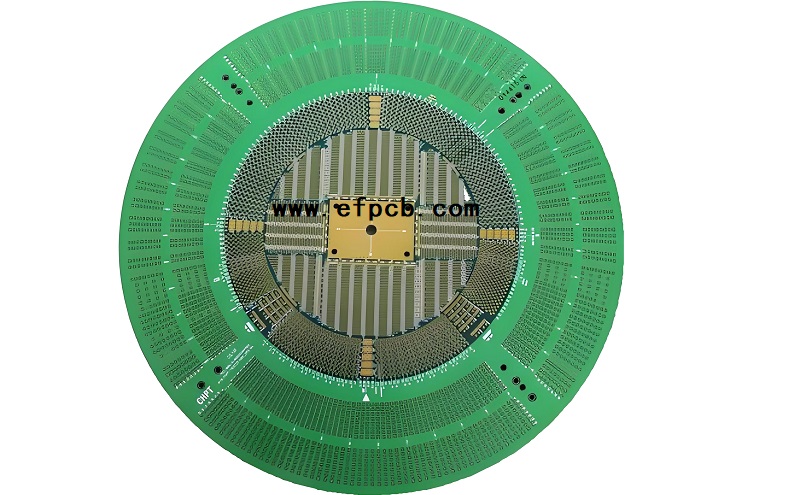

The semiconductor producing area comprises of four essential cycles: semiconductor plan, wafer handling, wafer bundling, and semiconductor testing. The testing system is separated into four classifications: wafer testing, end result testing, framework level testing, and consume in testing. Test cards, load sheets, and consume in sheets (Napkin) are a portion of the PCBs utilized with semiconductor test board. It is a tailormade item, and the related PCB should be uniquely crafted to match the chip's plan for testing.

These PCBs are known as semiconductor test sheets. It is a fundamental test consumable following chip bundling. It is generally utilized during the yield test stage. It is feasible to dispose of incomplete chips and lower the expense of the back-end process by surveying assuming the chip's capability, speed, unwavering quality, power utilization, and different attributes are ordinary. Squander and forestall rejecting last products attributable to breaking down incorporated circuits.

Test load board: A mechanical and electrical point of interaction that connections test gear to the gadget being tried. It is for the most part used in the yield test following IC bundling at the back finish of semiconductor creation. During this phase of testing, damaged parts may be eliminated to keep future electrical things from being disposed of attributable to broken ICs.

Test card: The test card interfaces the test machine to the pass on cushion during CP testing.

It is much of the time used as the actual connection point to the Heap load up. In specific conditions, the Test Card interfaces with the Heap board through an attachment or another connection point circuit. Before wafer cutting, the wafer quality might be checked utilizing a PC to forestall pressing costs for harmed things.

Chin-wiper (Consume in Load up): When the bundling test is done, the IC is exposed to a maturing test under exact working conditions and time requirements to guarantee its steadfastness. The Chin-wiper is a PCB board that is utilized to test the maturing of coordinated circuits.

Interposer: The Test card's sign is deciphered through the interposer go-between layer, permitting the test of the Test head to get the sign and effectively move it to the test machine for translation.

As semiconductor innovation progresses at a fast rate, so do the issues engage with testing. Makers are constantly attempting to make further developed semiconductor test board fit for taking care of more prominent velocities, more modest structure variables, and greater intricacy in semiconductor gadgets. Moreover, with the presentation of AI (ML) into semiconductor testing, there is a rising accentuation on mechanization and prescient investigation to expand efficiency and precision.

Notwithstanding, close by these headways come difficulties like expense, versatility, and similarity with arising advancements. Adjusting the requirement for far reaching testing with the tensions of time-to-market and cost limitations stays an interminable issue for semiconductor producers.

- 1Understanding UL 94V-0 Flammability Rating for Printed Circuit Boards (PCBs)

- 2Top 10 Flexible PCB Factories in 2025

- 3HDI PCB Market Outlook 2025: Future Prospects, Growth Analysis & Innovations

- 4HDI PCB Design Comprehensive Guide: Mastering High Density Interconnect Technology in 2025

- 5Top HDI PCB Manufacturers (2024)

- 6IC Substrate | Comprehensive Guide (2021)

- 7PCB core raw material CCL

- 8How to Make mSAP PCB?

- 9Top 10 IC Substrate Fabricators (2024)

- 10What is IPC 4761 Type VII Via in Pad PCB?

- Skype ID: shawnwang2006

- Phone No。: +86-755-23724206

- Email: sales@efpcb.com

- Quick Contact